# John McCarthy

## Recursive Functions of Symbolic Expressions and their Computation by Machine

### AIM-008 March 13, 1959

```

eval[e] =[

first[e]=NULL-\full[eval[first[rest[e]]]-)T; 1->F]

first[e] =ATOM-\[atom[eval[first[rest[e]]]]-T;1-F]

first[e] =EQ-eval[first[rest[e]]] =eval[first[rest[rest[e]]]] >T;

first[e] =QUOTE--)first[rest[e]];

first[e]=FIRST->first[eval[first[rest[e]]]];

first[e] =REST-rest[eval[first[rest[e]]]]

first[e] = COMBINE -> combine[eval[first[rest[e]]]; eval first[rest[rest

[e]]]]];

first[e] = COND -> evcon[rest[e]];

first[first[e]]=LAMBDA-evlam[first[rest[first[e]]];first[rest[rest

[first[e]]];rest[e]];

first[first[e]] =LABEL - eval[combine[subst[first[e];first[rest

[first[e]]];first[rest[rest[first[e]]]];rest[e]]]

where; evcon(c) = [eval[first[first[o]]]=1->eval[first[rest[first[c]]]];

T→evcon[rest[c]]]

```

## Первый Лисп

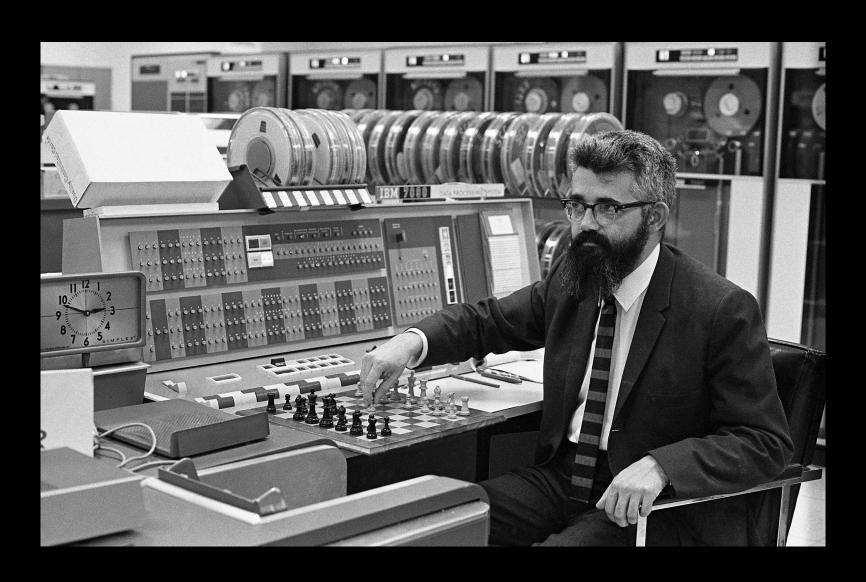

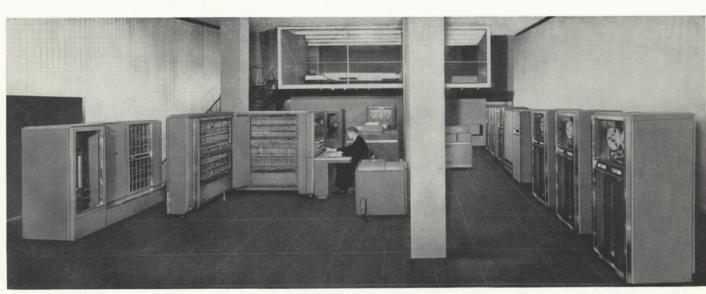

Стив Рассел пишет версию под ІВМ 704

Magnetic Core Storage

Central Processing Unit Magnetic Drum Operator's Console Power Supply Printer Card Reader Card Punch

Magnetic Tape Units

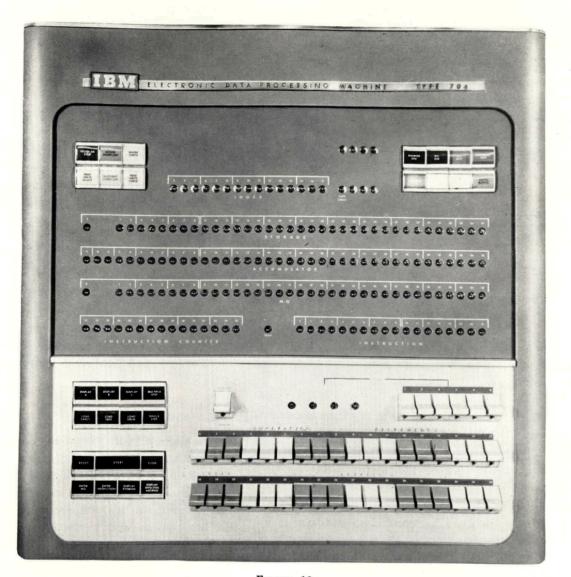

IBM 704 ELECTRONIC DATA-PROCESSING MACHINES

FIGURE 12

## **LISP 1.5**

#### LISP 1.5 Programmer's Manual

The Computation Center and Research Laboratory of Electronics

Massachusetts Institute of Technology

## Джозеф Ликлайдер

- «Симбиоз человека и комьютера» <u>1960</u>

- «Межгалактическая компьютерная сеть» >>

Стандартные компоненты, доступные всем, итп

# Project MAC

- MAC Mathematic and Computation, Multiple Access Computer, Machine Aided Cognition, Man and Machine

- Марвин Минский, Джон Маккарти, Джозеф Ликлайдер, Ричард Гринблатт, ...

- Компьютерное зрение, механическое движение, язык

- ARPANET

## MACLISP

- 1964

- PDP-10

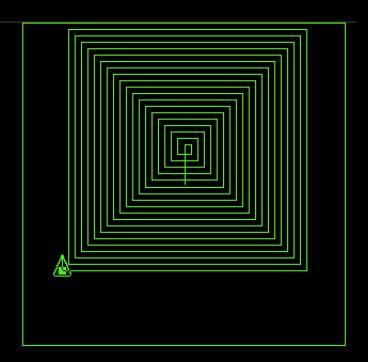

```

>30 spiral :n + 10

;CONTINUING EVALUATION

;YOU HAVE RUN OUT OF LIST SPACE. MORE?:

y

; OK. (19832 WORDS)

;ERROR IN LINE 10 OF SPIRAL: FORWARD :N

;TURTLE MOVED OFF THE TOP OF THE SCREEN

##MORE##

```

The LISP language is used widely in the artificial intelligence research community, and is rapidly gaining adherents outside this group. Most serious LISP usage has historically been on the DEC PDP-10 computer, and both "major" implementations (InterLisp at BBN/XEROX and Maclisp at M.I.T.) were originally done on the PDP-10. Our personal experience has largely been with the Maclisp dialect of LISP, which was originally written in 1965.

Over the years, dramatic changes have taken place in the Maclisp implementation. At a certain point, however, modification and reimplementation of a language on a given machine can no longer efficiently gloss over basic problems in the architecture of the computer system. We, and many others, believe this is now the case on the PDP-10 and similar time-shared computer systems.

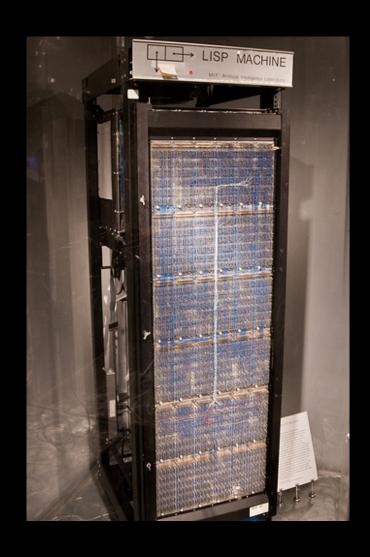

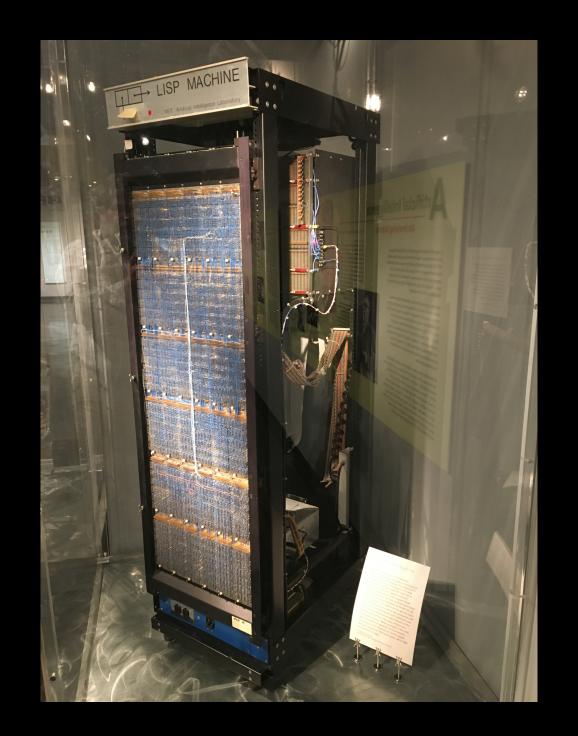

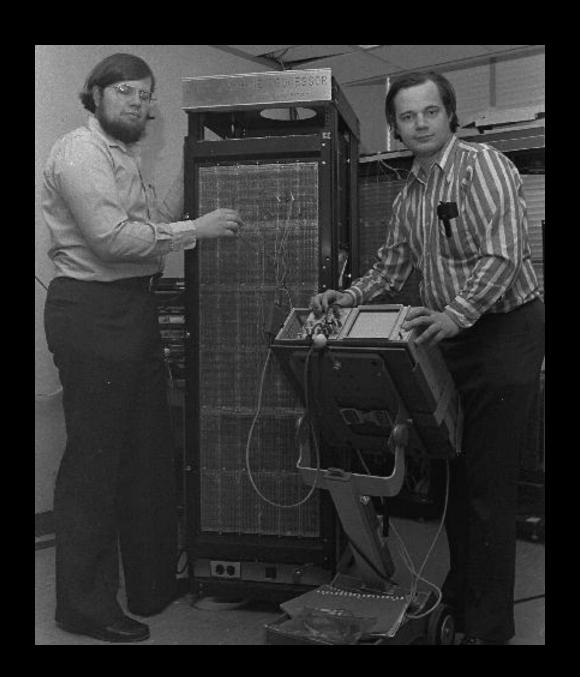

## CONS

"Knight machine"

#### **CURRENT STATUS (August 1977)**

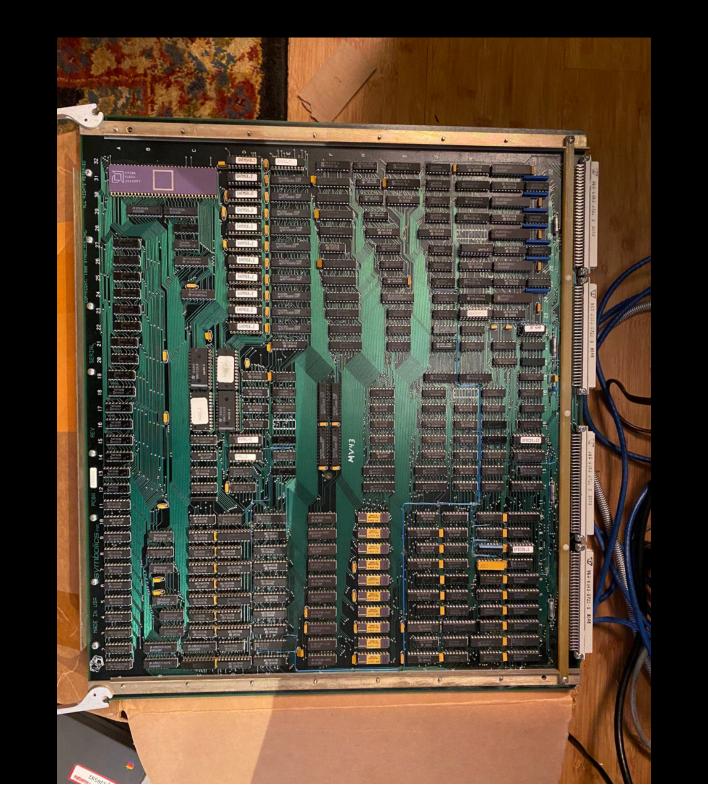

The original prototype CONS machine was designed and built somewhat more than two years ago. It had no memory and no I/O capability, and remained pretty much on the back burner while software was developed with a simulator on the PDP-10 (the simulator executed the Lisp machine macro instruction set, a function now performed by CONS microcode.) Microprogramming got under way a little over a year ago, and in the beginning of 1977 the machine got memory, a disk, and a terminal.

## Так зачем лисп машины?

- Fast call/return

- Memory efficient lists

- Garbage collector

- Dynamic type checking (tagged memory, hardware)

- Больше памяти!!1

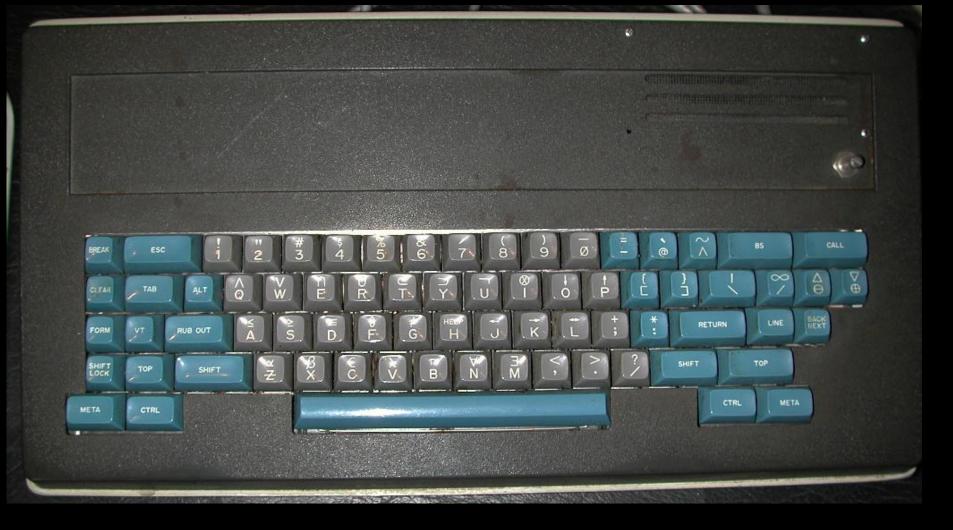

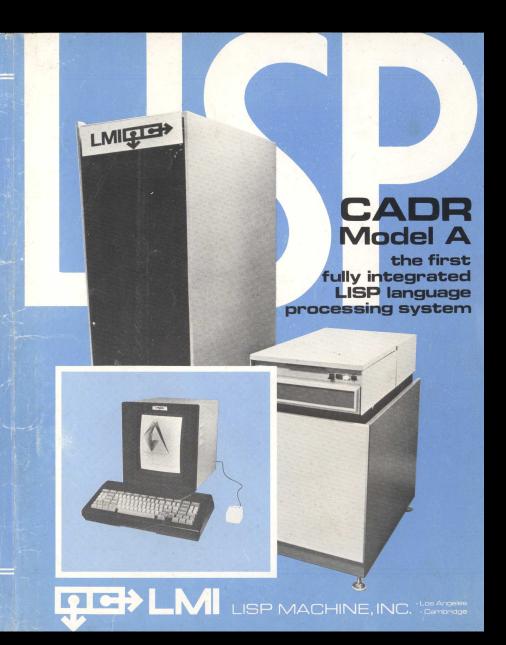

## CADR

- 32-bit, 1k RAM, 16k microcode 24-bit virtual addresses, etc.

- Монтаж накруткой

- Малое количество ИС

- 25 машин, \$50000 каждая

- CHAOS

## «Инерпретатор микрокода»

JUMP

ALU

BYTE

JUMP

DISPATCH

ALU The destination receives the result of a boolean or arithmetic operation performed on the two sources.

BYTE The destination receives the result of a byte extraction, byte deposit, or selective field substitution from one source to the other. The byte so manipulated can be of any non-zero width.

A transfer of control occurs, conditional on the value of any bit accessible to the M bus, or on a variety of ALU and other internal conditions such as pending interrupts and page faults.

DISPATCH A transfer of control occurs to a location determined by a word from the dispatch memory selected by a byte of up to seven bits extracted from the M bus.

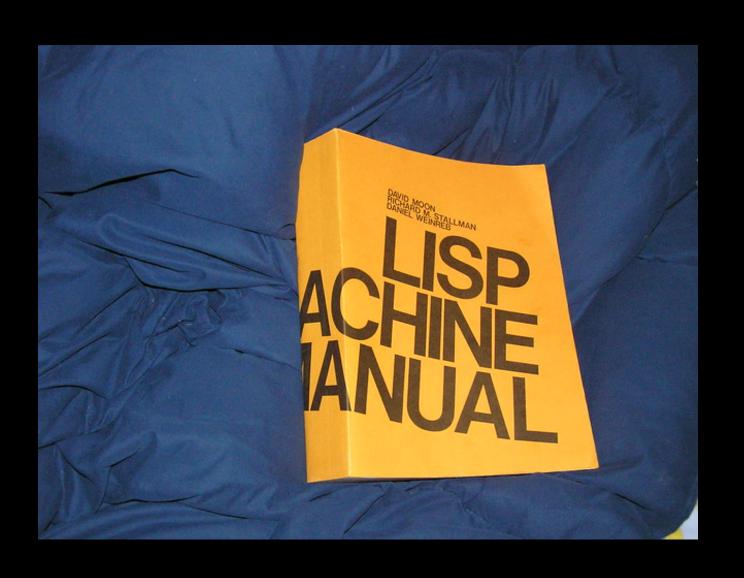

# CHINUAL

## Symbolics, LMI

- 1979

- Пилим бабло

- Russel Noftsker vs Richard Greenblatt

- GNU

LISP machines have been used extensively in the following areas:

- Natural Language Comprehension Human Factors Engineering

- Integrated Circuit Design

- Symbolic Mathematics

- Image Perception Processing

- Physical Simulation

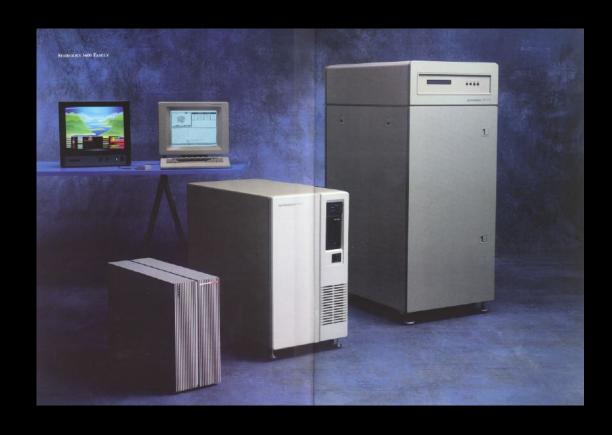

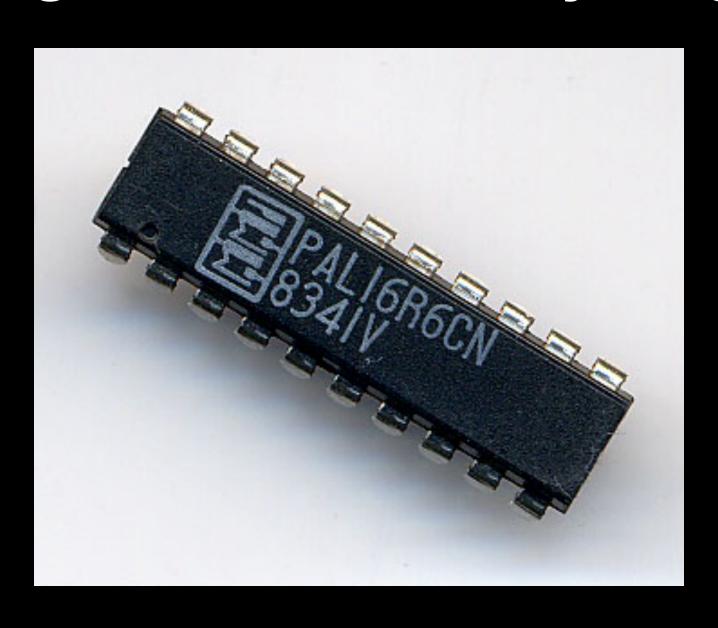

# Symbolics 3600

• CADR + PAL

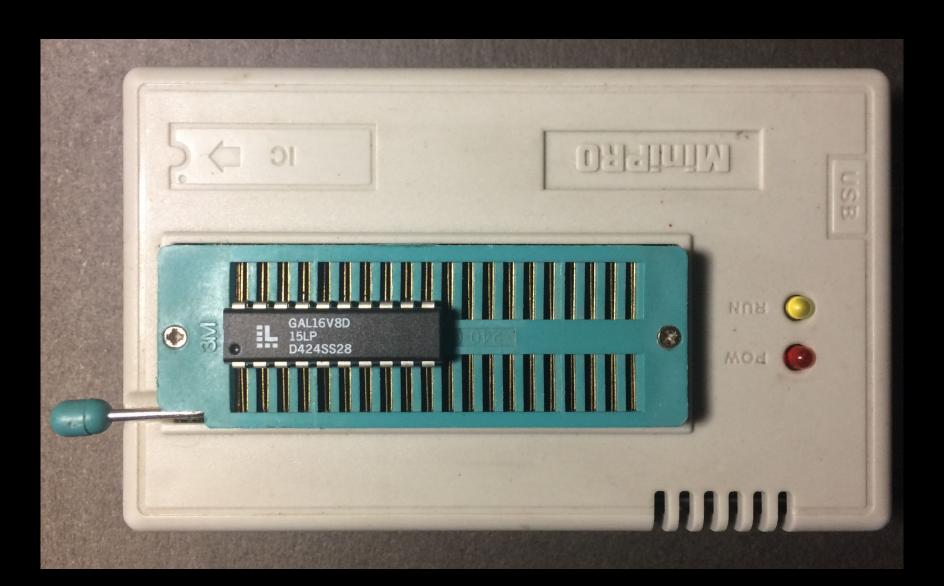

## Programmable Array Logic

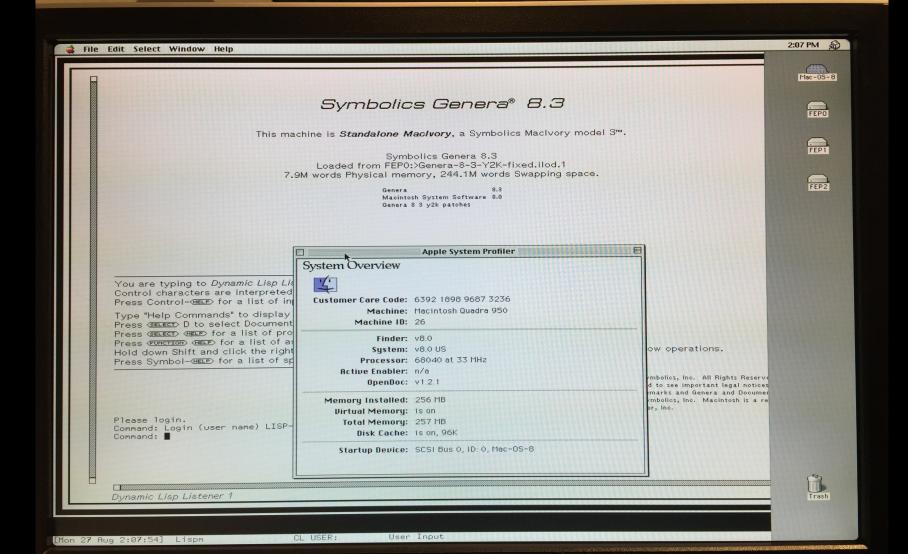

# XL1200, MacIvory

CADR + PAL+ VLSI (Ivory)

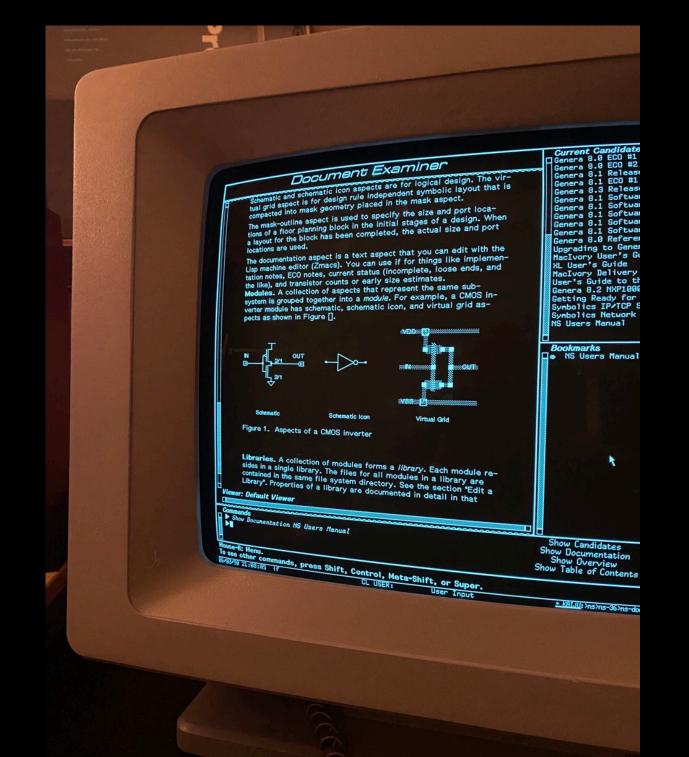

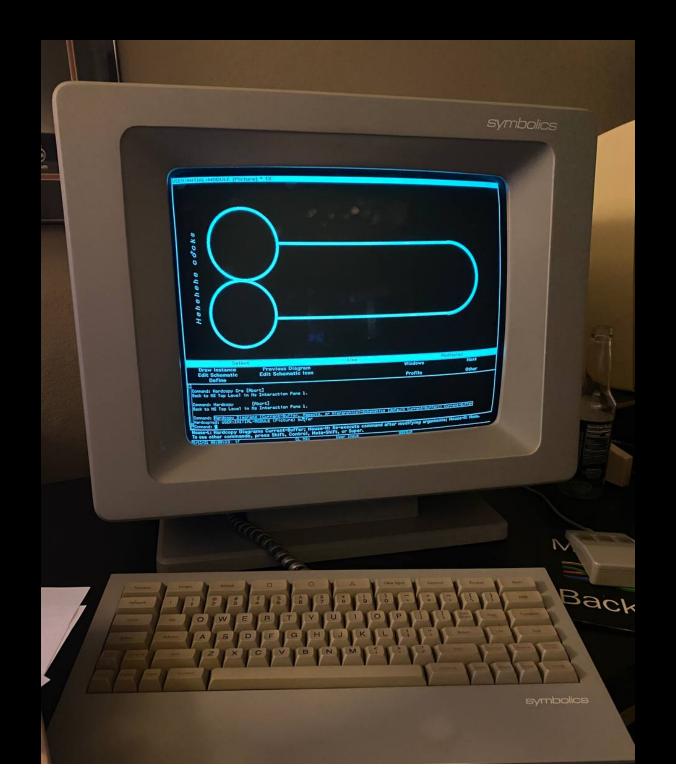

#### 3. VLSI Implementation

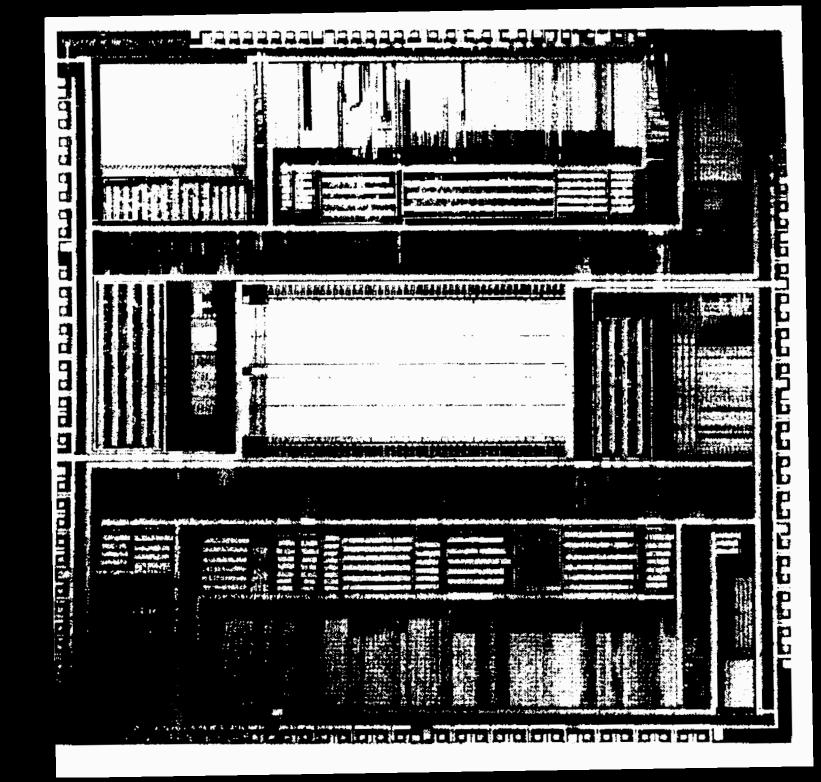

Ivory was designed using a highly integrated proprietary VLSI design system called NS [5], which is implemented on the Symbolics 3600 Lisp machine. This provides a highly interactive design and simulation environment and in addition, a symbolic layout methodology that allows the complete chip data base to be designed in a process independent manner. The current design is electrically optimized for a 2u/1.6u double level metal CMOS process, although the data base may be retargetted to 1.2u and 1.0u processes to decrease cost and increase speed. The layout density in all styles of layout is comparable to orthogonal geometry hand designs. The design contains approximately 390,000 transistor sites with 255,000 placements. A total elapsed time of 10 months was needed to progress from architecture specification to the first tape-out.

A two phase clock is employed which is routed throughout the chip. Registers and latches use nMOS pass transistors with restoring inverters as the basic storage device. An extra synchronization clock is used to generate memory timing signals.

In line with the ability to retarget the design using the symbolic layout tools and the sheer impossibility of hand optimizing 390,000 transistors, the circuit design of the chip was kept fairly simple. The majority of logic in the design is static - either fully complementary CMOS logic gates, pseudo nMOS gates for high fun-in NOR gates or nMOS pass transistor logic for selected muxes. Dynamic gates are only used in the microcode ROM, instruction decoder and the RAMs. The RAMs are implemented using a standard 6 transistor static cell, while the CAMs in the design use a 10 transistor static cell. All control logic is in the form of static, fully complementary standard cells. The symbolic layout for control modules was automatically generated using a standard cell place and route system. A standard cell library, memory library and data-path library is used for most of the designs in the chip. Customization of logic and circuits is kept to a minimum to ensure uniformity of